# **BREVET DE TECHNICIEN SUPÉRIEUR**

# SYSTÈMES ÉLECTRONIQUES

# **EPREUVE E4**

# Étude d'un Système Technique

Unité E4.1 - ÉLECTRONIQUE

SESSION 2013

Durée : 4 heures Coefficient : 4

#### Matériel autorisé :

- Toutes les calculatrices de poche y compris les calculatrices programmables, alphanumériques ou à écran graphique à condition que leur fonctionnement soit autonome et qu'il ne soit pas fait usage d'imprimante (Circulaire n°99-186, 16/11/1999).

Tout autre matériel est interdit.

#### Documents à rendre avec la copie :

- Documents réponse BR1 à BR4

#### Le sujet se compose de :

A- Analyse fonctionnelle du système : A1 à A12

B- Sujet:

Questionnaire :B1 à B6Documents réponse :BR1 à BR4DocumentationBAN1 à BAN21

Dès que le sujet vous est remis, assurez-vous qu'il est complet.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013  |

|-----------------------------------------------------------|-----------|---------------|

| U4.1 – Électronique                                       | 13SEE4EL1 | 36881011 2013 |

#### **ANALYSE FONCTIONNELLE**

# Présentation du Récepteur GPS/Traceur SIMRAD CP33

### Le système GPS

Le système GPS (Global Positioning System) est un système développé par l'armée américaine, dont le rôle est de :

- permettre à un utilisateur quelconque d'obtenir sa localisation en trois dimensions (latitude, longitude, altitude) par rapport à la surface terrestre,

- fournir une référence précise de temps.

Le système GPS est organisé en trois segments :

Segment Spatial, actuellement constitué de 30 satellites opérationnels transmettant des informations de manière permanente vers les utilisateurs. Ces satellites sont répartis sur 6 orbites d'une altitude d'environ 20 200 km par rapport à la surface terrestre. Chaque satellite possède une période de révolution de 11h58min sur son orbite. La position relative des satellites doit permettre à un utilisateur quelconque de recevoir simultanément les signaux issus d'au moins 4 d'entre eux (12 satellites, au maximum, peuvent être simultanément visibles par un utilisateur),

- Segment Utilisateur, constitué par les récepteurs GPS qui assurent la réception des informations issues de satellites de la flotte GPS et fournissent à leurs utilisateurs des informations de position et de temps après avoir décodé, exploité et mis en forme les informations fournies par les satellites GPS en vue,

- Segment Contrôle, constitué par 5 stations émettrices et réceptrices réparties sur la surface de la terre, de manière à ce que chaque satellite puisse être, en permanence, contrôlé par au moins une station. Les stations reçoivent les informations fournies par les satellites, effectuent des calculs de corrections sur les

paramètres relatifs à leurs orbites et renvoient ces informations vers les satellites. De plus, ces stations ont pour mission de vérifier l'état de fonctionnement de chacun des satellites.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A1/12 |

#### Le principe de fonctionnement du système GPS

Afin de déterminer la position d'un utilisateur, un récepteur GPS effectue la mesure de la distance entre sa position et la position de plusieurs satellites en mesurant le temps de parcours de l'onde électromagnétique émise par chaque satellite utilisé.

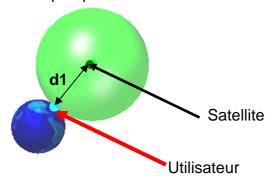

Considérons un satellite se trouvant à la distance d<sub>1</sub> d'un récepteur GPS. Cette information nous indique que l'utilisateur se trouve sur une sphère de rayon d<sub>1</sub> autour du satellite.

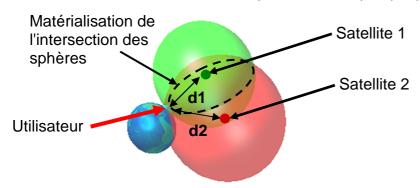

Considérons deux satellites se trouvant respectivement aux distances  $d_1$  et  $d_2$  d'un récepteur GPS. Ces deux informations nous indiquent que l'utilisateur se trouve à l'intersection de deux sphères, de rayons respectifs  $d_1$  et  $d_2$ . L'intersection de deux sphères étant un cercle, l'utilisateur sait donc qu'il se trouve quelque part sur ce cercle.

Considérons maintenant trois satellites se trouvant respectivement aux distances  $d_1$ ,  $d_2$  et  $d_3$  d'un récepteur GPS. Ces trois informations nous indiquent que l'utilisateur se trouve à l'intersection du cercle précédent et d'une sphère. Cette intersection est constituée de deux points, l'un à une distance aberrante par rapport à la terre, l'autre se trouvant à une distance cohérente. Ce dernier point constitue l'emplacement calculé par le récepteur GPS, qui sera fourni à l'utilisateur sous forme de latitude, longitude et altitude.

A partir de la mesure de ces trois distances, le récepteur GPS doit donc pouvoir calculer les trois informations de localisation suivantes :

- la longitude,

- la latitude,

- l'altitude.

À ces trois informations à déterminer s'ajoute une quatrième information constituée par l'erreur systématique  $\Delta d$  commise par un récepteur GPS donné sur les mesures de distances. Cette quatrième information nécessite l'acquisition des informations issues d'un quatrième satellite. Par conséquent, la présence de quatre satellites est indispensable à la localisation par GPS.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle               | 13SEE4EL1 | Page : A2/12 |

#### Les informations transmises par les satellites GPS au segment utilisateur

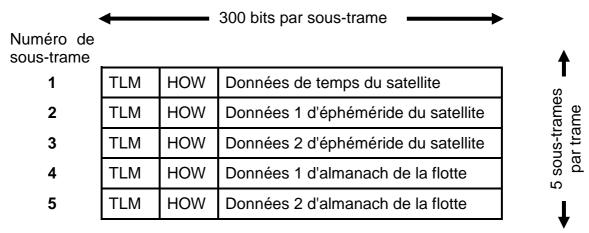

Chaque satellite transmet des informations de deux natures différentes :

- **Données de temps** du satellite émetteur (date et heure), fournies au sein de la soustrame 1, le contenu identique dans chaque trame,

- **Éphéméride**: informations qui sont propres au satellite émetteur (coordonnées courantes du satellite, informations relatives à sa trajectoire, état du satellite...), fournies au sein des deux sous-trames consécutives 2 et 3, le contenu identique dans chaque trame,

- **Almanach** : informations concernant l'ensemble des satellites de la flotte GPS, fournies au sein de 25 trames consécutives. Les spécifications GPS assurent une validité de ces informations pendant une durée minimale de 60 jours. Elles sont rectifiées régulièrement par le segment contrôle.

Les données de navigation sont transmises par chaque satellite, avec un débit de 50 bits/seconde, au sein de trames organisées de la manière suivante :

- une trame est constituée de 1 500 bits répartis dans 5 sous-trames,

- une sous-trame est constituée de 300 bits répartis en 10 mots de 30 bits.

Toutes les sous-trames commencent chacune par les mots TLM (Telemetry) et HOW (Hand Over Word).

#### Structure du mot TLM

#### **TLM**

| Préambule<br>1000 1011 | Donnée  | Parité |

|------------------------|---------|--------|

| 8 bits                 | 26 bits | 6 bits |

Le préambule du mot TLM permet à un récepteur GPS d'identifier le début d'une sous-trame et de se synchroniser.

#### Structure du mot HOW

#### **HOW**

| 11011                 |                      |        |

|-----------------------|----------------------|--------|

| Temps dans la semaine | Numéro de sous-trame | Parité |

|                       | 30u3-traine          |        |

| 17 bits               | 3 bits               | 6 bits |

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle               | 13SEE4EL1 | Page : A3/12 |

#### Remarques:

- les informations temporelles indispensables à un récepteur GPS se trouvent principalement dans la sous-trame 1 de n'importe quelle trame,

- les informations d'almanach permettent à un récepteur GPS de connaitre entre autres, lorsqu'on le met en service, la référence des satellites susceptibles d'être visibles. Ces informations sont, en général, mémorisées de manière permanente dans les récepteurs GPS, ce qui permet de diminuer la durée au bout de laquelle celui-ci est capable d'effectuer une localisation,

- les informations complètes d'almanach sont réparties dans les sous-trames 4 et

5 de 25 trames successives. Il est donc nécessaire d'effectuer l'acquisition de 25 trames successives pour qu'un récepteur GPS charge l'ensemble de ces informations.

#### La modulation des informations transmises par les satellites GPS

Tous les satellites de la flotte GPS émettent leurs informations avec deux porteuses identiques pour chaque satellite :

- une porteuse de fréquence 1 575,42 MHz, transmettant des informations dites

« L1, code C/A » fournissant une faible précision, destinées aux applications grand public,

- une porteuse de fréquence 1 226,7 MHz, transmettant des informations dites

« L2, code P » fournissant une grande précision, destinées aux applications militaires.

Afin d'identifier un satellite parmi les autres, les données transmises par chaque satellite sont associées à un code qui lui est propre.

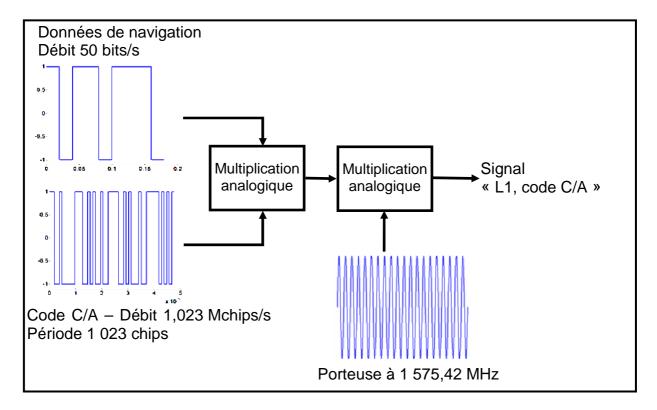

Pour les informations « L1, code C/A », on utilise un code binaire pseudo-aléatoire. Ce code est constitué d'une succession de 1 023 chips<sup>(1)</sup> se répétant périodiquement. Il est transmis avec un débit de 1,023 Mchips/s.

Les données de navigation, quant à elles, sont transmises au rythme de 50 bits/s.

Les données de navigation et le code C/A sont combinés et viennent moduler la porteuse de fréquence 1 575,42 MHz en phase, réalisant ainsi une modulation BPSK, qui est une modulation numérique de phase à deux états.

Note (1) : Pour faire la différence entre les données de navigation transmises par un satellite <u>GPS et l</u>e code pseudo-aléatoire qui lui est associé, **chaque bit du code pseudo-aléatoire est dénommé « chip »**.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A4/12 |

#### Constitution de l'information « L1, code C/A » transmise par un satellite GPS

Ce principe de modulation permettant d'utiliser une porteuse unique pour des émetteurs différents (ici, les satellites) identifiés par un code dont le débit est bien supérieur à celui des informations utiles à transmettre fait partie des **modulations à étalement de spectre** (modulations CDMA).

Comme son nom l'indique, une modulation à étalement de spectre entraîne un accroissement très important de l'occupation spectrale du signal modulé CDMA, par rapport à l'occupation spectrale du signal utile en bande de base.

Cette modulation permet d'apporter une solution à l'encombrement des bandes fréquentielles liées à la multiplicité croissante des sources émettrices dans tous les domaines d'applications utilisant des ondes hertziennes (radiodiffusion, télédiffusion, télécommunications mobiles, WiFi, Bluetooth, ...) puisque de nombreuses sources peuvent utiliser la même fréquence porteuse, à condition d'utiliser des codes différents.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A5/12 |

#### Le Récepteur GPS/Traceur SIMRAD CP33

Le Récepteur GPS/Traceur SIMRAD CP33 est un appareil destiné à la navigation maritime permettant de :

- déterminer et visualiser la position du bateau sur le globe terrestre,

- programmer le parcours du bateau, en association avec un pilote automatique,

- échanger des informations avec d'autres appareils destinés à la navigation maritime.

#### **Entrées**

- **OEM**: onde électromagnétique modulée CDMA, de fréquence porteuse 1 575,42MHz, caractéristique de la bande GPS « L1, code C/A »,

- **Informations de cartes C-MAP**: informations issues d'un lecteur de cartes C-MAP fournissant une cartographie,

- Commandes manuelles : appuis sur les touches de la face avant par l'utilisateur.

#### **Sorties**

- Informations visuelles : images couleur destinées à l'utilisateur.

#### Entrées/Sorties

- Informations au format NMEA0183: ce format est défini dans la norme internationale d'échange d'informations basé sur une liaison série asynchrone. Ces informations sont échangées avec d'autres appareils destinés à la navigation maritime,

- **Informations au format SIMNET**: format propriétaire d'échange d'informations basé sur un bus CAN étendu. Ces informations sont échangées avec d'autres appareils destinés à la navigation maritime.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A6/12 |

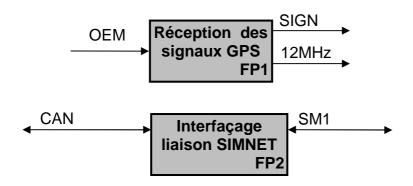

# Schéma fonctionnel partiel de 1<sup>er</sup> degré du Récepteur GPS/Traceur SIMRAD CP33

L'étude portera sur les deux fonctions présentées ci-dessous.

#### **Description des fonctions principales**

#### FP1: Réception des signaux GPS

Réalise l'acquisition des signaux issus des satellites de la flotte GPS visibles, et transpose ces signaux vers une fréquence porteuse plus faible.

#### **Entrée**

- OEM : onde électromagnétique modulée CDMA de fréquence porteuse 1 575,42 MHz caractéristique de la bande GPS « L1, code C/A ».

#### **Sorties**

- SIGN : signal modulé CDMA de fréquence porteuse 3,42 MHz,

- 12MHz : signal périodique de fréquence 12 MHz, utilisé pour l'échantillonnage du signal SIGN par un ASIC.

#### FP2: Interfaçage liaison SIMNET

Réalise la conversion d'informations série au format électrique compatible CMOS en informations série au format SIMNET.

#### Entrée/Sortie

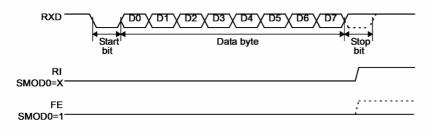

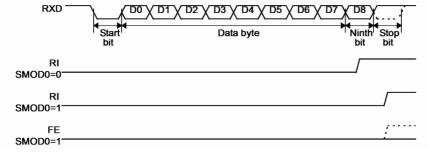

- SM1 : liaison série asynchrone au format électrique compatible CMOS, fournie par un microcontrôleur (4800 bits/s – Un bit Stop – Pas de parité).

- CAN : liaison série du réseau SIMNET, basé sur la norme Bus CAN (Identifiant sur 29 bits Débit 250 kbits/s).

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A7/12 |

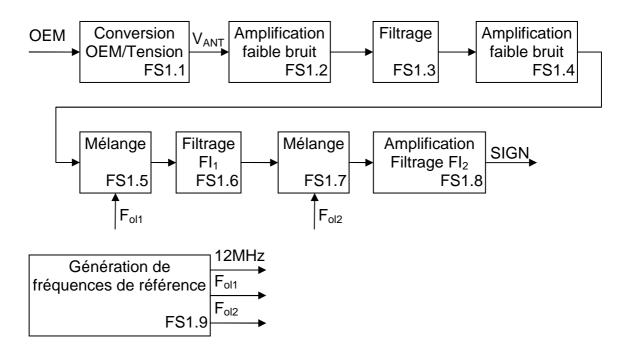

# Schéma fonctionnel de 2ème degré de la fonction FP1

### Description des fonctions secondaires de FP1

#### FS1.1: Conversion OEM/Tension

#### **Entrée**

- OEM : onde électromagnétique modulée CDMA, de fréquence porteuse 1 575,42 MHz caractéristique de la bande GPS « L1, code C/A ».

#### **Sortie**

V<sub>ANT</sub>: signal électrique, image de l'onde électromagnétique reçue.

#### FS1.2: Amplification faible bruit

Réalise l'amplification du signal d'entrée, en ajoutant le moins de bruit possible.

#### Entrée:

- V<sub>ANT</sub> : signal électrique, image de l'onde électromagnétique reçue.

#### Sortie:

- signal amplifié, image de l'onde électromagnétique reçue.

#### FS1.3: Filtrage

Sélectionne la fréquence centrale et la largeur de bande utile du spectre d'entrée.

#### Entrée:

- signal amplifié, image de l'onde électromagnétique reçue.

#### Sortie:

- signal filtré dans la bande de fréquences utiles d'entrée.

#### FS1.4: Amplification faible bruit

Réalise l'amplification du signal filtré, en ajoutant le moins de bruit possible.

#### Entrée :

- signal filtré dans la bande de fréquences utiles d'entrée.

#### Sortie:

- signal électrique filtré dans la bande de fréquences utiles d'entrée, amplifié.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A8/12 |

#### FS1.5 : Mélange

Effectue la multiplication du signal filtré avec le signal de sortie de l'oscillateur local, de fréquence F<sub>ol1</sub>.

#### Entrées :

- signal filtré dans la bande de fréquences utiles d'entrée, amplifié.

- signal sinusoïdal de fréquence Fol1.

#### Sortie:

- signal issu du mélange des signaux d'entrée.

#### FS1.6: Filtrage Fl<sub>1</sub>

Effectue le filtrage du signal d'entrée autour de la fréquence intermédiaire Fl<sub>1</sub>.

#### Entrée:

- signal issu du mélange des signaux d'entrée de FS1.5.

#### Sortie:

- signal filtré autour de la fréquence intermédiaire Fl<sub>1</sub>.

#### FS1.7 : Mélange

Effectue la multiplication du signal filtré autour de la fréquence intermédiaire Fl<sub>1</sub> avec le signal de sortie de l'oscillateur local, de fréquence F<sub>ol2</sub>.

#### Entrées :

- signal filtré autour de la fréquence intermédiaire Fl<sub>1</sub>,

- signal sinusoïdal de fréquence F<sub>ol2</sub>.

#### Sortie:

- signal issu du mélange des signaux d'entrée.

### FS1.8 : Amplification Filtrage FI<sub>2</sub>

Effectue le filtrage et l'amplification du signal d'entrée autour de la fréquence intermédiaire Fl<sub>2</sub>.

#### Entrée:

- signal issu du mélange des signaux d'entrée de FS1.7.

#### Sortie:

- signal amplifié et filtré autour de la fréquence intermédiaire Fl<sub>2</sub>.

#### FS1.9 : Génération de fréquences de référence.

Génère les signaux périodiques nécessaires au fonctionnement de la réception des signaux GPS.

#### Sorties:

- 12MHz : signal rectangulaire de fréquence 12 MHz,

- F<sub>ol1</sub> : signal sinusoïdal de fréquence F<sub>ol1</sub>,

- F<sub>ol2</sub>: signal sinusoïdal de fréquence F<sub>ol2</sub>.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d        | Session 2013 |              |

|---------------------------------------------|--------------|--------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A9/12 |

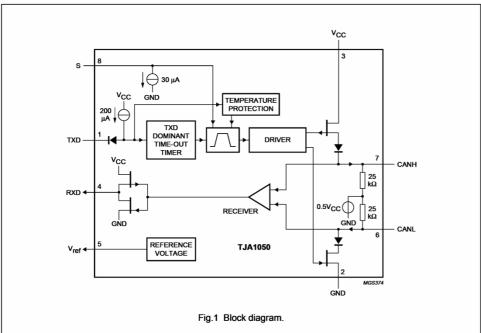

#### **SPECIFICATIONS DU BUS CAN**

Le réseau de transmission d'informations SIMNET est un réseau propriétaire (SIMRAD) basé sur un bus CAN, version 2.B (champ d'identifiant sur 29 bits).

Le bus CAN est un bus de transmission d'informations, bidirectionnel et différentiel, composé physiquement de deux lignes dénommées CANH et CANL :

- Les niveaux des signaux sont fonction de la différence de potentiel entre ces deux lignes,

- les niveaux logiques ne sont pas définis par des états '0' ou '1', mais par des états récessifs ou dominants.

La constitution d'une trame CAN étendue (identifiant sur 29 bits) est donnée ci-dessous :

| Start of frame (SOF) | Champ<br>d'arbitrage | Champ de contrôle | Champ de données           | Champ<br>CRC | Champ<br>d'acquittement | End of<br>frame<br>(EOF) |

|----------------------|----------------------|-------------------|----------------------------|--------------|-------------------------|--------------------------|

| 1 bit<br>dominant    | 32 bits              | 6 bits            | 8 octets<br>pour<br>SIMNET | 16 bits      | 2 bits                  | 7 bits<br>récessifs      |

De plus, le détail du contenu du champ d'arbitrage est le suivant :

| Poids fort de l'identifiant | SRR   | IDE   | Poids faible de l'identifiant | RTR   |

|-----------------------------|-------|-------|-------------------------------|-------|

| 11 bits                     | 1 bit | 1 bit | 18 bits                       | 1 bit |

- SRR (Substitute Remote Request): 1 bit récessif,

- IDE (Identifier Extension bit): 1 bit récessif,

- RTR (Remote Transmission Request): 1 bit dominant pour une trame de données et récessif pour une trame de requête.

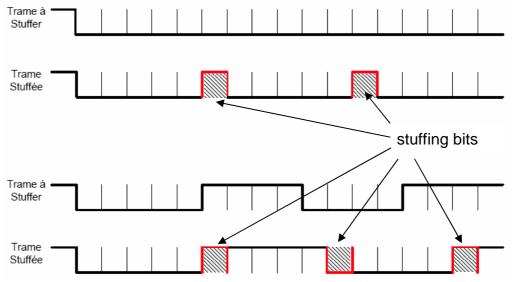

D'autre part, après 5 états consécutifs identiques dans un message, un bit supplémentaire est ajouté, d'état inverse à ces 5 états consécutifs. Ceci permet d'éviter de laisser la ligne à un niveau constant trop longtemps. Ces bits supplémentaires sont appelés bits de remplissage ou « stuffing bits ».

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |                |

|---------------------------------------------|--------------|----------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | P age : A10/12 |

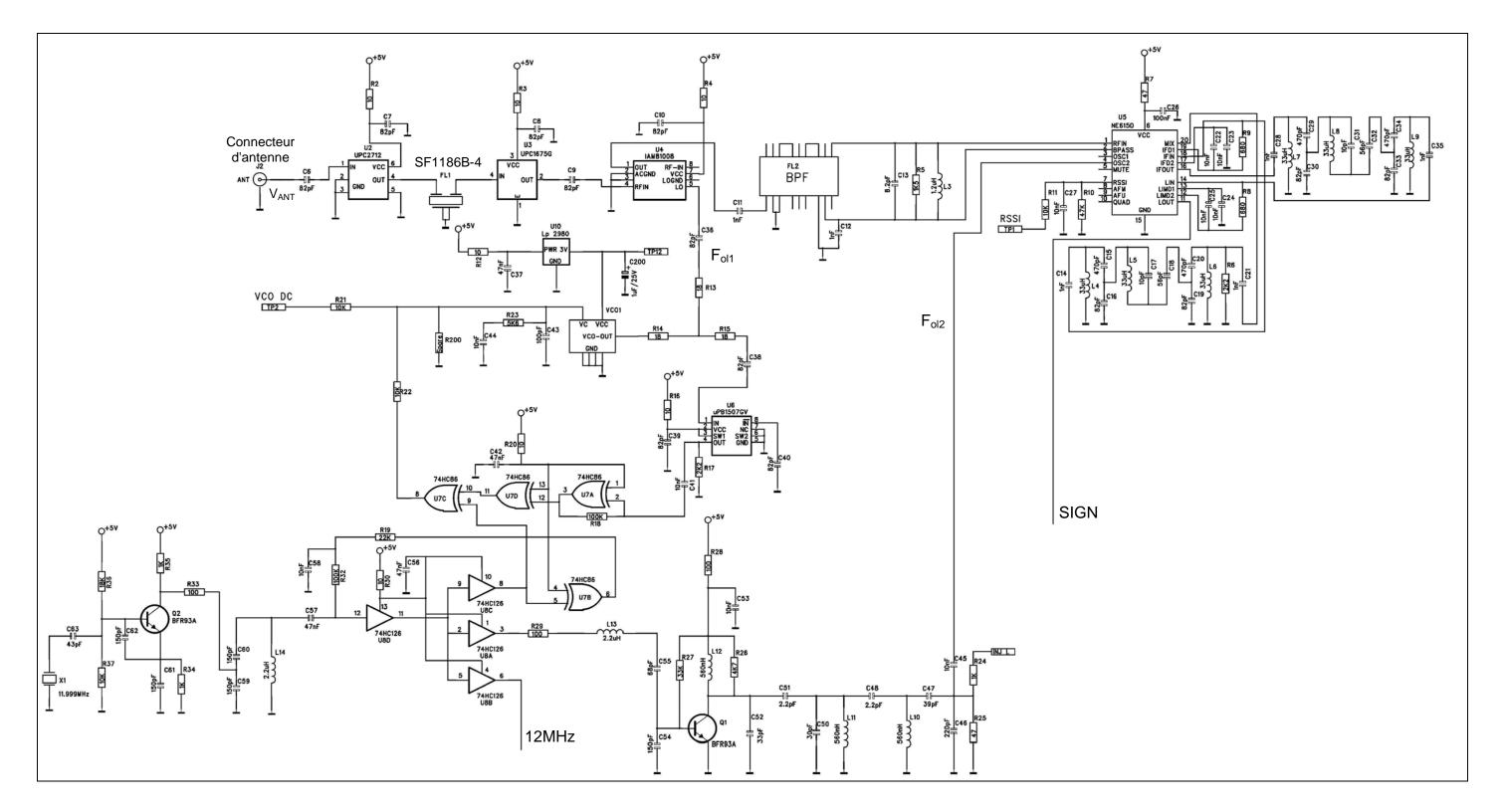

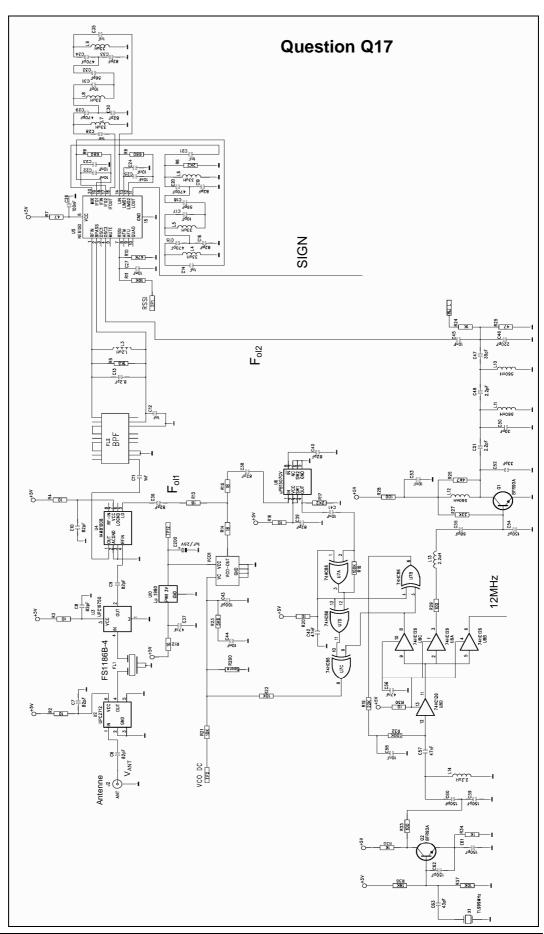

Schéma structurel de la fonction FP1

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |               |

|---------------------------------------------|--------------|---------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A11/12 |

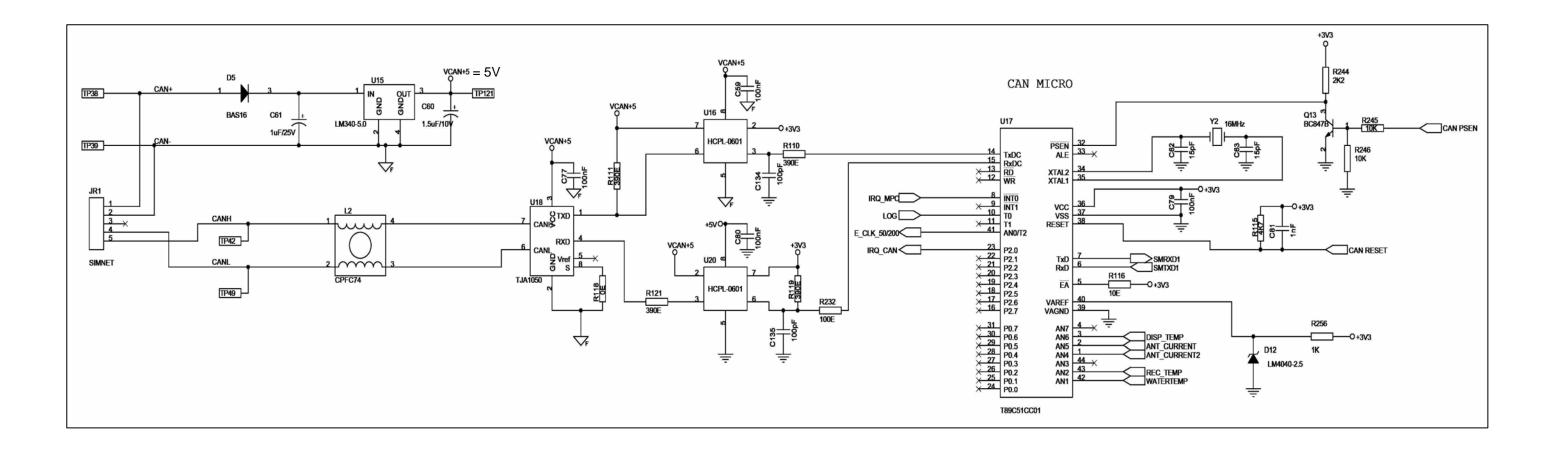

Schéma structurel de la fonction FP2

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o        | Session 2013 |               |

|---------------------------------------------|--------------|---------------|

| U4.1 – Électronique – Analyse Fonctionnelle | 13SEE4EL1    | Page : A12/12 |

#### SUJET

Les parties A, B et C du sujet sont indépendantes. Les réponses aux questions sont à rendre sur feuilles d'examen. Les documents réponse sont à rendre dans tous les cas avec la copie, même s'ils n'ont pas été remplis.

### **PARTIE A: Analyse fonctionnelle**

# A1 : Durées de propagation et d'acquisition des informations issues d'un satellite

Compte tenu de son mouvement, la distance d'un satellite par rapport à un utilisateur quelconque peut varier entre 20 200 km et 25 820 km.

La vitesse de propagation des ondes électromagnétiques est  $c = 3.10^8$  m/s. Les ondes se propagent en ligne droite à travers l'atmosphère.

**Q1.** Calculer les valeurs extrêmes du temps de propagation des ondes transmises par les satellites.

À partir des informations fournies en pages A3 et A4 du dossier d'analyse fonctionnelle :

- **Q2.** Déterminer le nombre minimal de trames GPS permettant d'acquérir une information complète de temps, d'almanach et d'éphéméride émise par un satellite unique.

- **Q3.** Calculer le nombre de bits nécessaires à l'acquisition d'une information complète de temps, d'almanach et d'éphéméride d'un satellite unique.

- **Q4.** Déduire, du résultat précédent, la durée correspondant à l'acquisition d'une information complète de temps, d'almanach et d'éphéméride d'un satellite unique.

Les fabricants de récepteurs GPS implémentent l'almanach en usine, si bien que seule l'acquisition de l'éphéméride peut s'avérer nécessaire pour obtenir un positionnement correct.

- **Q5.** Déterminer le nombre de sous-trames nécessaires à l'acquisition des données de temps d'un satellite unique. Indiquer le nombre de bits correspondants.

- **Q6.** Déterminer le nombre de sous-trames nécessaires à l'acquisition complète des données d'éphéméride d'un satellite unique. Indiquer le nombre de bits correspondants.

- **Q7.** Déterminer le nombre de sous-trames nécessaires à l'actualisation des données de temps et d'éphéméride d'un satellite unique. Indiquer le nombre de bits correspondants.

- **Q8.** Calculer la périodicité d'actualisation des informations de temps et d'éphéméride.

- **Q9.** Relever dans la documentation technique (documents BAN2 et BAN3), le taux de mise à jour des informations GPS du récepteur, spécifié par le constructeur.

Les questions précédentes montrent une différence importante entre la périodicité d'actualisation et le taux de mise à jour, géré par le récepteur GPS entre 2 actualisations.

**Q10.** Indiquer le temps maximum nécessaire à un récepteur GPS pour indiquer une information cohérente après un redémarrage.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o | Session 2013 |             |

|--------------------------------------|--------------|-------------|

| U4.1 – Électronique – Sujet          | 13SEE4EL1    | Page : B1/6 |

# A2 : Caractéristiques fréquentielles des informations traitées par le Récepteur GPS/Traceur SIMRAD CP33

À partir des informations fournies en pages A4 et A5 du dossier d'analyse fonctionnelle, et de la documentation du Récepteur GPS/Traceur SIMRAD CP33 (document BAN3) :

Q11. Indiquer la fréquence de la porteuse qui est traitée par ce récepteur.

Sachant que l'occupation spectrale correspondant à la transmission de bits ou de chips de durée Tb est égale à  $\frac{2}{Tb}$ :

- Q12. Calculer l'occupation spectrale des informations de navigation du GPS.

- Q13. Calculer l'occupation spectrale du code C/A.

- Q14. Déduire, de ces deux derniers résultats, l'occupation spectrale du signal modulé « L1, code C/A » et justifier la dénomination « modulation à étalement de spectre ».

- Q15. Expliquer l'intérêt d'utiliser ce type de modulation.

# PARTIE B : Étude de FP1 - Réception des signaux GPS

#### **B1: Généralités**

- **Q16.** Indiquer le nom donné à un dispositif de réception basé sur le schéma fonctionnel de 2<sup>ème</sup> degré de la fonction FP1 (dossier d'analyse fonctionnelle, pages A8 et A9).

- **Q17.** Délimiter, sur le schéma structurel de la fonction FP1 (document réponse BR4), les fonctions secondaires FS1.2 à FS1.9.

#### Remarques:

- On pourra s'aider des documentations des composants IAM81008 (document BAN4) et NE615D (document BAN5).

- Un schéma structurel plus lisible est également fourni, page A11 du dossier d'analyse fonctionnelle.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Sujet                               | 13SEE4EL1 | Page : B2/6  |

# B2 : Étude de la génération de fréquences de référence

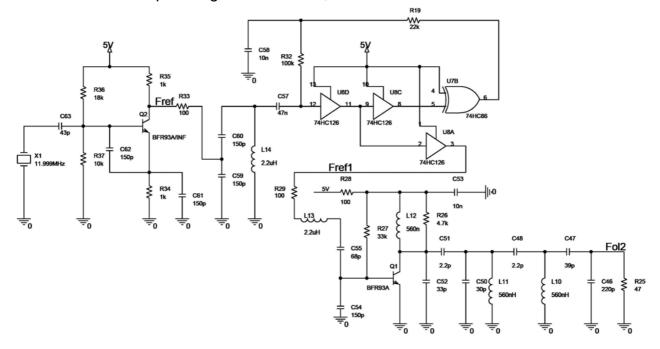

Cette fonction (FS1.9) fournit deux fréquences,  $F_{ol1}$  et  $F_{ol2}$ , obtenues par multiplications de la fréquence délivrée par un oscillateur construit autour du transistor Q2. La structure étudiée pour la génération de  $F_{ol2}$  est la suivante :

- **Q18.** Indiquer la référence du composant qui impose une fréquence d'environ 12 MHz à l'oscillateur.

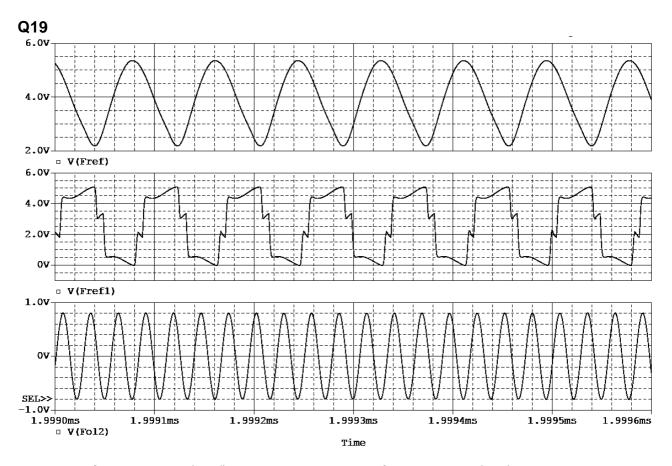

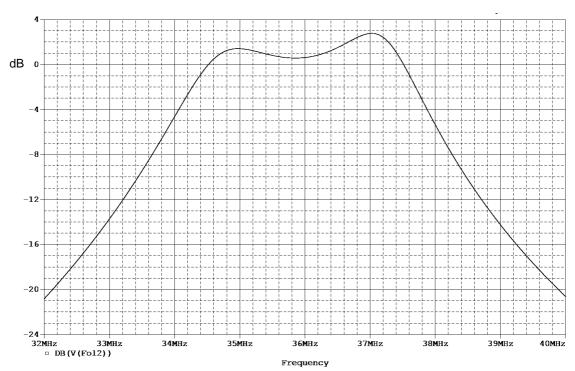

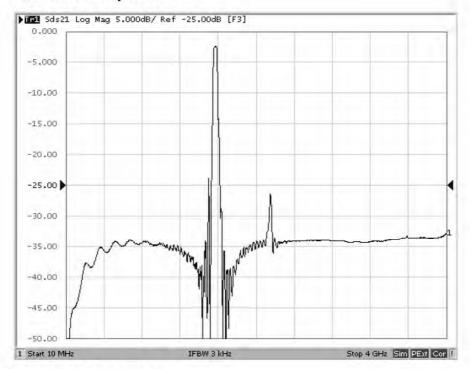

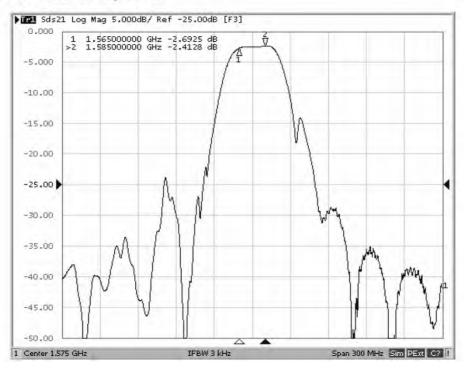

- **Q19.** Déterminer et indiquer sur le document réponse BR1, en faisant clairement apparaître la méthode utilisée, les fréquences des signaux repérés V(Fref) et V(Fol2) du relevé précédent.

- **Q20.** Indiquer la relation simple qui existe entre les valeurs des fréquences F<sub>ref</sub> et F<sub>ol2</sub>.

La courbe de réponse fréquentielle du filtre se trouvant entre les points repérés Fref1 et Fol2 sur le schéma ci-dessus est donnée document réponse BR1.

- **Q21.** Relever, en les repérant sur la courbe, la fréquence centrale et la bande passante à -3 dB de ce filtre.

- **Q22.** Expliquer le principe sur lequel est basée la production du signal F<sub>ol2</sub> et justifier la présence des circuits logiques 74HC126.

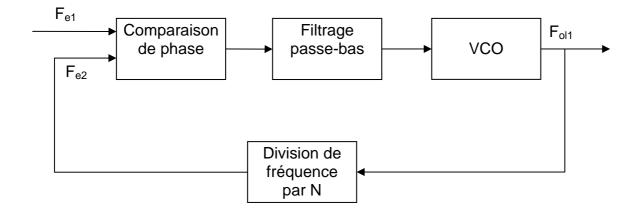

La génération de la fréquence  $F_{ol1}$  est réalisée grâce à une boucle à verrouillage de phase dont le schéma fonctionnel simplifié est le suivant :

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Sujet                               | 13SEE4EL1 | Page : B3/6  |

- **Q23.** Donner la relation existant entre les fréquences d'entrée F<sub>e1</sub> et F<sub>e2</sub> lorsque la boucle à verrouillage de phase est verrouillée.

- **Q24.** Déduire du résultat précédent la relation existant entre les fréquences F<sub>e1</sub> et F<sub>ol1</sub> lorsque la boucle à verrouillage de phase est verrouillée.

- **Q25.** Indiquer, en utilisant le schéma structurel de la fonction FP1 (page A11 du dossier d'analyse fonctionnelle), la référence des composants réalisant la comparaison de phase.

- **Q26.** Indiquer, de même, la référence du composant réalisant la division de fréquence par N.

- **Q27.** Déterminer, à l'aide de la documentation du composant uPB1507GV (documents BAN9 et BAN10) et du schéma structurel de la fonction FP1 (page A11 du dossier d'analyse fonctionnelle), le taux N de division de ce composant.

- **Q28.** Déduire des résultats précédents la valeur de la fréquence F<sub>ol1</sub>.

- **Q29.** Calculer la valeur de la fréquence intermédiaire (notée FI<sub>1</sub>) en sortie de la fonction FS1.5.

- **Q30.** Déterminer la fréquence appelée fréquence image F<sub>im</sub> du signal qui, présent en entrée du récepteur, provoquerait un signal de même fréquence intermédiaire.

- **Q31.** Montrer que le composant SF1186B-4 (documents BAN13 et BAN14) réalisant la fonction FS1.3 permet d'éliminer les signaux de fréquence F<sub>im</sub>.

# B3 : Étude de la chaîne d'amplification et filtrage

Les spécifications des satellites GPS précisent que la puissance des signaux reçus sur la surface de la terre doit être supérieure à -130 dBm.

Il est donc indispensable de réaliser une amplification de puissance sur ce signal avant de le démoduler.

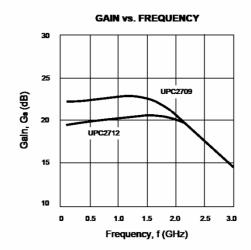

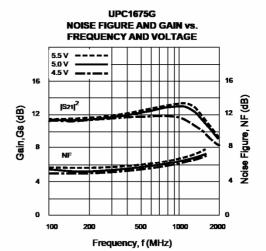

- Q32. Relever, dans les documentations des composants UPC2712 (document BAN11) et UPC1675G (document BAN12), l'amplification minimale de puissance et la fréquence de coupure à -3dB de chacun d'eux.

- Q33. Relever, dans la documentation constructeur du filtre SF1186B-4 (documents BAN13 et BAN14), l'atténuation maximale à la fréquence de travail et la bande passante à -3 dB.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Sujet                               | 13SEE4EL1 | Page : B4/6  |

**Q34.** Déduire, des résultats précédents, les valeurs du gain minimal total et de la bande passante totale à -3dB de l'association des fonctions FS1.2 – FS1.3 – FS1.4.

La puissance reçue sur l'antenne est égale à -130 dBm.

- **Q35.** Calculer, en dBm, la puissance présente en sortie de la fonction FS1.4 et reporter cette valeur dans le tableau correspondant du document réponse BR2.

- **Q36.** Donner la relation existant entre une puissance exprimée en dBm et la même puissance exprimée en Watts.

- Q37. Calculer, en Watts, les valeurs de la puissance reçue sur l'antenne et de la puissance de sortie de la fonction FS1.4. Reporter ces valeurs dans le tableau correspondant du document réponse BR2.

L'impédance de référence du récepteur GPS est égale à 50Ω.

**Q38.** Calculer la valeur efficace de la tension à l'entrée de la fonction FS1.2 et en sortie de la fonction FS1.4. Reporter ces valeurs dans le tableau correspondant du document réponse BR2.

# PARTIE C : Étude de FP2 – Interfaçage liaison SIMNET

Le schéma structurel de cette fonction est fourni page A12 du dossier d'analyse fonctionnelle. Les informations relatives au fonctionnement du bus CAN sont données page A10 du dossier d'analyse fonctionnelle.

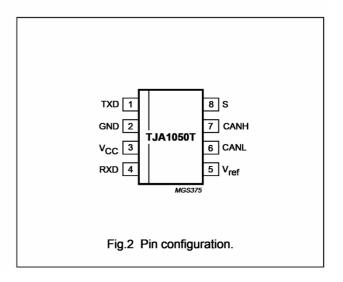

Le rôle du composant TJA1050 (U18) est d'effectuer l'interfaçage entre le Bus CAN du réseau SIMNET et le microcontrôleur T89CS51CC001 (U17).

#### C1 : Étude de la conversion niveaux SIMNET ↔ Niveaux CMOS

- Q39. Rechercher, en utilisant la documentation du composant TJA1050 (documents BAN15 à BAN17), les valeurs typiques des niveaux de tension correspondant respectivement à un état récessif et à un état dominant sur chacune des lignes CANL et CANH puis reporter ces valeurs dans le tableau correspondant du document réponse BR2.

- **Q40.** Déterminer, à partir du tableau 1 du document BAN16, la correspondance entre les niveaux logiques des broches RXD et TXD et les états du bus CAN, puis reporter ces résultats dans le tableau correspondant du document réponse BR2.

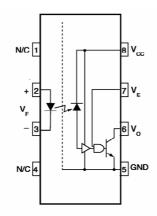

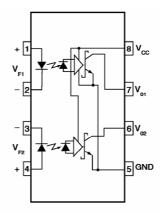

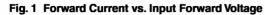

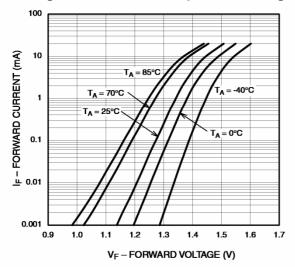

La documentation du composant HCPL-0601 est donnée documents BAN18 et BAN19.

- Q41. Calculer l'intensité minimale du courant circulant dans la résistance R121 pour chaque état logique de la broche RXD (on considère qu'un niveau logique '0' correspond une tension VRXD ≈ 0V). Reporter cette valeur dans le tableau correspondant du document réponse BR2.

- **Q42.** Justifier la présence de la résistance R119 associée au composant U20.

- Q43. Calculer, pour chacun des niveaux logiques de la broche RXD du composant TJA1050 (U18), les valeurs de la tension ramenée sur la broche RxDC du composant T89C51CC01 (U17) ainsi que les niveaux logiques correspondants. Reporter ces résultats dans le tableau du document réponse BR2.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Sujet                               | 13SEE4EL1 | Page : B5/6  |

#### C2 : Analyse d'une trame SIMNET

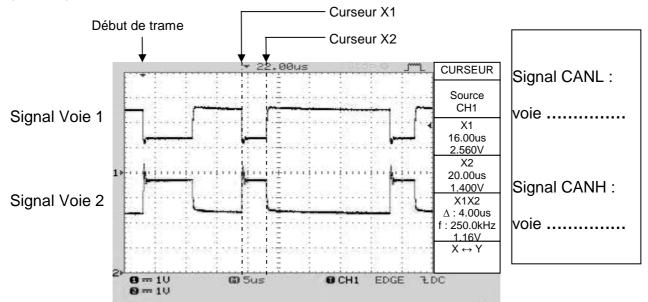

Lors de la réception de messages GPS, une des trames SIMNET élaborées par le Traceur/GPS SIMRAD CP33 a été isolée et visualisée sur un oscilloscope sur le document réponse BR2.

- **Q44.** Mesurer la durée élémentaire d'un état (durée délimitée par des curseurs). En déduire la valeur du débit binaire correspondant et reporter ces valeurs sur le document réponse BR2.

- **Q45.** Indiquer, sur le document réponse BR2, à partir du relevé et en exploitant la documentation du composant TJA1050 (document BAN17), le numéro de voie correspondant respectivement aux signaux CANL et CANH.

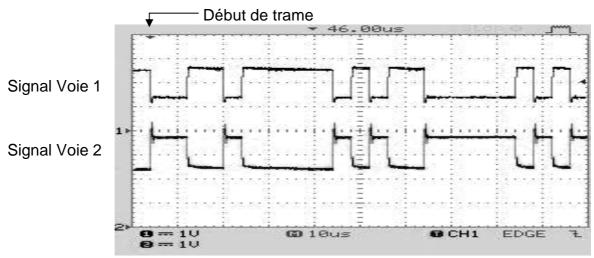

Pour les questions suivantes, il est admis que, sur le relevé du document réponse BR3, la voie 1 correspond à CANL et la voie 2 à CANH.

- **Q46.** Relever, à partir du chronogramme fourni document réponse BR3, l'état (Dominant ou Récessif) associé à chacun des bits de la trame relevée et reporter ces valeurs dans le tableau 1 (on représentera un état dominant par 'D' et un état récessif par 'R').

- Q47. Encadrer, dans le tableau 1 du document réponse BR3, les bits de remplissage (« Stuffing Bits »).

- **Q48.** Remplir le tableau 2 du document réponse BR3 après avoir éliminé les bits de remplissage et en remplaçant les états dominants ou récessifs par les niveaux logiques '0' ou '1' associés.

- **Q49.** Compléter, à partir des questions précédentes, le tableau 3 du document réponse BR3, en indiquant les 5 premiers caractères (exprimés en hexadécimal) représentant l'identifiant de la trame relevée (en regroupant les bits conformément aux délimiteurs imposés).

#### C3: Programmation du microcontrôleur T89C51CC01 (U17)

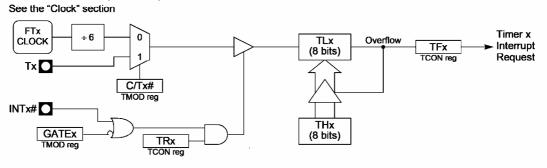

Le microcontrôleur de la fonction FP2 dialogue avec un microcontrôleur central. Il élabore et transmet les informations au réseau SIMNET par l'intermédiaire du composant TJA1050. Un extrait du programme de configuration de l'UART (document BAN20) et du Timer1 (document BAN21) est fourni document réponse BR3.

- **Q50.** Préciser le mode de fonctionnement du Timer1 imposé par l'instruction TMOD = 0x20.

- **Q51.** Expliquer le rôle de l'instruction TCON = 0x40.

- Q52. L'expression du débit binaire de l'UART ainsi configurée est :

$$D\acute{e}bit (bits/s) = \frac{Fosc}{32 \times 12 \times (256 - TH1)}$$

, où  $Fosc$  est la fréquence du quartz associé

au microcontrôleur (voir schéma structurel, page A12 du dossier d'analyse fonctionnelle) et *TH*1 est le contenu initial du Timer1. Sachant que l'on désire un débit binaire de 9600 bits/s, calculer la valeur de *TH*1 et compléter l'élément de programme fourni dans le document réponse BR3 en exprimant la valeur obtenue en hexadécimal.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013 |

|-----------------------------------------------------------|-----------|--------------|

| U4.1 – Électronique – Sujet                               | 13SEE4EL1 | Page : B6/6  |

# **DOCUMENT RÉPONSE**

Fréquence de V(Fref) : ...... Fréquence de V(F<sub>ol2</sub>) : .....

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o   | Session 2013 |              |

|----------------------------------------|--------------|--------------|

| U4.1 – Électronique – Document réponse | 13SEE4EL1    | Page : BR1/4 |

# Q35, Q37, Q38

|                                    | Entrée de la   | Sortie de la   |

|------------------------------------|----------------|----------------|

|                                    | fonction FS1.2 | fonction FS1.4 |

| Puissance (dBm)                    | -130           |                |

| Puissance (W)                      |                |                |

| Valeur efficace de la tension (µV) |                |                |

#### **Q39**

|                   | État ré    | ecessif    | État dominant |            |  |  |  |  |  |

|-------------------|------------|------------|---------------|------------|--|--|--|--|--|

|                   | Ligne CANL | Ligne CANH | Ligne CANL    | Ligne CANH |  |  |  |  |  |

| Valeur typique    |            |            |               |            |  |  |  |  |  |

| de la tension (V) |            |            |               |            |  |  |  |  |  |

Q40

| Niveau sur le bus CAN | Niveau logique sur<br>les broches<br>RXD ou TXD |

|-----------------------|-------------------------------------------------|

| État récessif         |                                                 |

| État dominant         |                                                 |

Q41, Q43

| Niveau logique de RXD | Intensité du courant<br>dans R121 (mA) | Tension en<br>RxDC (V) | Niveau logique de RxDC |

|-----------------------|----------------------------------------|------------------------|------------------------|

| <b>'0'</b>            |                                        |                        |                        |

| <b>'1'</b>            |                                        |                        |                        |

#### Q44 et Q45

Durée d'un bit : ...... µs Débit binaire :.....kbits/s

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d   | Session 2013 |              |

|----------------------------------------|--------------|--------------|

| U4.1 – Électronique – Document réponse | 13SEE4EL1    | Page : BR2/4 |

### Q46, Q47, Q48, Q49

#### Tableau 1

| Ét | États récessifs (R) ou dominants (D) de la trame CAN ci-dessus |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----|----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|    |                                                                |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

### Tableau 2

| Nive | Niveau logique des bits successifs de la trame, après avoir éliminé les bits de remplissage |     |     |     |     |     |     |     |            |     |            |     |     |            |     |             |            |            |            |            |

|------|---------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|------------|-----|------------|-----|-----|------------|-----|-------------|------------|------------|------------|------------|

| SOF  | 129                                                                                         | 128 | 127 | 126 | 125 | 124 | 123 | 122 | <b>I21</b> | 120 | <b>I19</b> | SRR | IDE | <b>I18</b> | 117 | <b>I</b> 16 | <b>I15</b> | <b>I14</b> | <b>I13</b> | <b>I12</b> |

|      |                                                                                             |     |     |     |     |     |     |     |            |     |            |     |     |            |     |             |            |            |            |            |

|      |                                                                                             |     |     |     |     |     |     |     |            |     |            |     |     |            |     |             |            |            |            |            |

| Tableau 3                                             | Rec | Reconstitution du début de l'identifiant de la trame proposée |     |     |     |     |     |     |            |     |            |     |     |     |     |     |            |

|-------------------------------------------------------|-----|---------------------------------------------------------------|-----|-----|-----|-----|-----|-----|------------|-----|------------|-----|-----|-----|-----|-----|------------|

| Valeurs des bits                                      | 129 | 128                                                           | 127 | 126 | 125 | 124 | 123 | 122 | <b>I21</b> | 120 | <b>I19</b> | I18 | 117 | I16 | 115 | 114 | <b>I13</b> |

| Valeur<br>hexadécimale de<br>chaque groupe de<br>bits |     |                                                               |     |     |     |     |     |     |            |     |            |     |     |     |     |     |            |

# Q50, Q51 et Q52

```

// Configuration du Timer1

TMOD = 0x20;

// Initialisation du Timer1

TH1 = .....; // À compléter

TL1 = TH1;

TCON = 0x40;

```

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o   | Session 2013 |              |

|----------------------------------------|--------------|--------------|

| U4.1 – Électronique – Document réponse | 13SEE4EL1    | Page : BR3/4 |

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d   | Session 2013 |              |

|----------------------------------------|--------------|--------------|

| U4.1 – Électronique – Document réponse | 13SEE4EL1    | Page : BR4/4 |

# **DOCUMENTATION TECHNIQUE**

# **Sommaire**

| Traceur/GPS SIMRAD CP33 | BAN2 à BAN3   |

|-------------------------|---------------|

| IAM81008                | BAN4 à BAN5   |

| NE615D                  | BAN6 à BAN8   |

| uPB1507GV               | BAN9 à BAN10  |

| UPC2712                 | BAN11         |

| UPC1675G                | BAN12         |

| Filtre SF1186B-4        | BAN13 à BAN14 |

| TJA1050                 | BAN15 à BAN17 |

| HCPL0601                | BAN18 à BAN19 |

| T89C51CC01 : UART       | BAN20         |

| T89C51CC01 : TIMER1     | BAN21         |

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o | Session 2013 |                |

|--------------------------------------|--------------|----------------|

| U4.1 – Électronique – Documentation  | 13SEE4EL1    | Page : BAN1/21 |

# **GPS/Traceur SIMRAD CP33** pour navigation maritime

# **Caractéristiques**

#### Généralités

Tension

d'alimentation: 12 et 24 V CC (10 à 32 V CC max) 8 à 17 watt

Câble

d'alimentation: Câble alimentation/NMEA, 2 m (Réf. 153-6070-002) Dimensions: H:144 mm (5.8") L:252 mm (10") P:70 mm (2.8")

Poids: 1,5 kg (3.3 lbs)

Environnement: -10 à +55°C, IEC 60945, étanche selon les normes USC 46

CFR et IP55

Boîtier: Arrière en aluminium moulé, face avant en polycarbonate

Ecran: TFT couleur rétroéclairé: 5.7" 320 x 240 pixels, ou.....

STN monochrome transflectif 6" 320 x 240 pixels

Présentation: 4 pages. Manuel, commutateur externe dédié, et séquence-

ment automatique.

Interface: 1 port entrée/sortie NMEA 0183

1 port SimNet / NMEA 2000 Transfert PC: WPL et RTE

Alarme - sortie signal 5 V, 50 mA

Fusible: T6.3A temporisé (5x20 mm)

#### Réseau SimNet

| Nombre maximum de produits connectés sur le réseau:  | 50                    |

|------------------------------------------------------|-----------------------|

| Longueur maximum du câblage (sans les 30m du capteur | r vent): 120 m (400') |

| Vitesse bus:                                         | 250 kbit/seconde      |

| Courant maximum dans une prise SimNet:               | 5A                    |

| Alimentation SimNet:                                 | 10.8 - 15 VDC         |

| Longueur maximum d'un câble dérivé:                  | 6 m (20')             |

| Longueur maximum de tous les câbles dérivés:         | 60 m (200')           |

| Etanchéité câblage:                                  | IP66                  |

| Température:                                         |                       |

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o          | Session 2013 |                |

|-----------------------------------------------|--------------|----------------|

| U4.1 – Électronique – Documentation 13SEE4EL1 |              | Page : BAN2/21 |

**Section GPS**

Récepteur: 14 canaux parallèles, code C/A, Filtre de Kalman 8 étages

Précision: Position (DGPS): 2 à 5 m RMS

Position (SDGPS): 3 à 7 m RMS

Position (GPS): 8 m RMS

Vitesse: 0.1 nœud

Cap: 1°

Filtre vitesse: 10 niveaux

Taux de mise

à jour: Intervalle 1 seconde, typique

Résistance

dynamique: Vélocité: 600 km/h

Accélération: 10 m / s<sup>2</sup>

Antenne GPS RS5640 Antenne DGPS MGL-3

Type: Quadrifilaire Helix Patch et H-field

Dimensions: L:230 mm H:75 mm

Ø:38 mm P:127 mm

Poids: 150 g (0.33 lbs) 600 g (1.3 lbs)

Environnement: -35°C à +75°C, humidité relative: 95%

Fixation: sur filetage 1" 14 (standard US)

Câble: RG58 10 m (standard), RG223 15 m (option), max. 30 m RG213

#### **Section traceur**

Systeme carto-

graphique: C-MAP NT+

Présentation: Carte semi dual - deux cartes à échelle et niveaux de détails

spécifiques

Mémoire interne: Enregistrement dynamique avec capacité de combinaison

jusqu'à

35,000 marques ou waypoints

10,000 waypoints avec nom (25 caractères)

50,000 points de tracés 50,000 sections de lignes

1,000 routes

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013   |

|-----------------------------------------------------------|-----------|----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN3/21 |

# Silicon Bipolar MMIC 5 GHz Active Double Balanced Mixer/IF Amp

# **Technical Data**

#### IAM-81008

#### **Features**

- RF-IF Conversion Gain From 0.05-5 GHz

- IF Conversion Gain From DC to 1 GHz

- Low Power Dissipation: 65 mW at V<sub>cc</sub> = 5 V Typical

- Single Polarity Bias Supply: V<sub>CC</sub> = 4 to 8 V

- Load-insensitive Performance

- Conversion Gain Flat Over Temperature

- Low LO Power Requirements:

-5 dBm Typical

- Low Cost Plastic Surface Mount Package

Typical applications include frequency down conversion, modulation, demodulation and phase detection. Markets include fiber-optics, GPS satelite navigation, mobile radio, and battery powered communications receivers.

The IAM series of Gilbert multiplier-based frequency converters is fabricated using HP's 10 GHz, f<sub>T</sub>, 25 GHz f<sub>MAX</sub> ISOSAT<sup>TM</sup>-I silicon bipolar process. This process uses nitride self alignment, submicrometer lithography, trench isolation, ion implantation, gold metallization and polyimide intermetal dielectric and scratch protection to achieve excellent performance, uniformity and reliability.

#### **Plastic SO-8 Package**

#### **Pin Configuration**

#### Description

The IAM-81008 is a complete low power consumption, double balanced active mixer housed in a miniature low cost plastic surface mount package. It is designed for narrow or wide bandwidth commercial and industrial applications having RF inputs up to 5 GHz. Operation at RF and LO frequencies less than 50 MHz can be achieved using optional external capacitors to ground. The IAM-81008 is particularly well suited for applications that require load-insensitive conversion and good spurious signal suppression with minimum LO and bias power consumption.

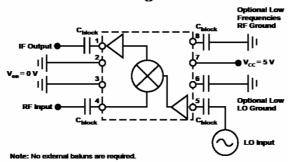

# Typical Biasing Configuration and Functional Block Diagram

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013   |

|-----------------------------------------------------------|-----------|----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN4/21 |

IAM-81008 Absolute Maximum Ratings

| Parameter Absolute Maximum       |              |

|----------------------------------|--------------|

| Device Voltage                   | 10 V         |

| Power Dissipation <sup>2,3</sup> | 300 mW       |

| RF Input Power                   | +14 dBm      |

| LO Input Power                   | +14 dBm      |

| Junction Temperature             | 150°C        |

| Storage Temperature              | −65 to 150°C |

| Thermal Resistance:                   |  |

|---------------------------------------|--|

| $\theta_{jc} = 80^{\circ} \text{C/W}$ |  |

#### Notes

- 1. Permanent damage may occur if any of these limits are exceeded.

- 2.  $T_{CASE} = 25^{\circ}C$ .

- 3. Derate at 4.4 mW/°C for  $T_C > 82^{\circ} C$  .

IAM-81008 Part Number Ordering Information

| Part Number   | Devices Per Reel | Reel Size |

|---------------|------------------|-----------|

| IAM-81008-TR1 | 1000             | 7"        |

For more information, see "Tape and Reel Packaging for Semmiconductor Devices".

# IAM-81008 Electrical Specifications $^{[1]},\,T_{_A}=25^{\circ}C$

| Symbol               | Parameters and Test Conditions: $V_{cc} = 5 \text{ V}$ , $Z_0 = 50 \Omega$ , $LO = -5 \text{ dBm}$ , $RF = -20 \text{ dBm}$ |                             | Units | Min. | Тур.  | Max. |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|------|-------|------|

| $G_{\mathbb{C}}$     | Conversion Gain                                                                                                             | RF = 2 GHz, LO = 1.75 GHz   | dΒ    | 6.0  | 8.5   | 10   |

| F <sub>3 dB</sub> RF | RF Bandwidth (G <sub>C</sub> 3 dB Down)                                                                                     | IF = 250  MHz               | GHz   |      | 3.5   |      |

| F <sub>3 dB</sub> IF | IF Bandwidth (G <sub>C</sub> 3 dB Down)                                                                                     | LO = 2 GHz                  | GHz   |      | 0.6   |      |

| P <sub>1 dB</sub>    | IF Output Power at 1 dB Gain Compression                                                                                    | RF = 2 GHz, LO = 1.75 GHz   | dBm   |      | -6    |      |

| IP <sub>3</sub>      | IF Output Third Order Intercept Point                                                                                       | RF = 2 GHz, $LO = 1.75 GHz$ | dBm   |      | 3     |      |

| NF                   | SSB Noise Figure                                                                                                            | RF = 2 GHz, LO = 1.75 GHz   | dB    |      | 17    |      |

|                      | RF Port VSWR                                                                                                                | f = 0.05 to 3.5 GHz         |       |      | 1.5:1 |      |

| VSWR                 | LO Port VSWR                                                                                                                | f = 0.05 to 3.5 GHz         |       |      | 2.0:1 |      |

|                      | IF Port VSWR                                                                                                                | f < 1 GHz                   |       |      | 1.5:1 |      |

| RFif                 | RF Feedthrough at IF Port                                                                                                   | RF = 2 GHz, LO = 1.75 GHz   | dBc   |      | -25   |      |

| LOif                 | LO Leakage at IF Port                                                                                                       | LO = 1.75 GHz               | dBm   |      | -25   |      |

| LO <sub>rf</sub>     | LO Leakage at RF Port                                                                                                       | LO = 1.75 GHz               | dBm   |      | -30   |      |

| Icc                  | Supply Current                                                                                                              |                             | mA    | 10   | 13    | 16   |

#### Note:

1. The recommended operating voltage range for this device is 4 to 8 V. Typical performance as a function of voltage is on the following page.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude o | Session 2013 |                |

|--------------------------------------|--------------|----------------|

| U4.1 – Électronique – Documentation  | 13SEE4EL1    | Page : BAN5/21 |

Philips Semiconductors Product specification

#### High performance low power mixer FM IF system

**NE/SA615**

#### DESCRIPTION

The NE/SA615 is a high performance monolithic low-power FM IF system incorporating a mixer/oscillator, two limiting intermediate frequency amplifiers, quadrature detector, muting, logarithmic received signal strength indicator (RSSI), and voltage regulator. The NE/SA615 combines the functions of Signetics' NE602 and NE604A, but features a higher mixer input intercept point, higher IF bandwidth (25MHz) and temperature compensated RSSI and limiters permitting higher performance application. The NE/SA615 is available in 20-lead dual-in-line plastic, 20-lead SOL (surface-mounted miniature package) and 20-lead SSOP (shrink small outline package).

The NE/SA605 and NE/SA615 are functionally the same device types. The difference between the two devices lies in the guaranteed specifications. The NE/SA615 has a higher I<sub>CC</sub>, lower input third order intercept point, lower conversion mixer gain, lower limiter gain, lower AM rejection, lower SINAD, higher THD, and higher RSSI error than the NE/SA615. Both the NE/SA605 and NE/SA615 devices will meet the EIA specifications for AMPS and TACS cellular radio applications.

For additional technical information please refer to application notes AN1994, 1995 and 1996, which include example application diagrams, a complete overview of the product, and artwork for reference.

#### **FEATURES**

- Low power consumption: 5.7mA typical at 6V

- Mixer input to >500MHz

- Mixer conversion power gain of 13dB at 45MHz

- Mixer noise figure of 4.6dB at 45MHz

- XTAL oscillator effective to 150MHz (L.C. oscillator to 1GHz local oscillator can be injected)

- 102dB of IF Amp/Limiter gain

- 25MHz limiter small signal bandwidth

- Temperature compensated logarithmic Received Signal Strength Indicator (RSSI) with a dynamic range in excess of 90dB

- Two audio outputs muted and unmuted

- Low external component count; suitable for crystal/ceramic/LC filters

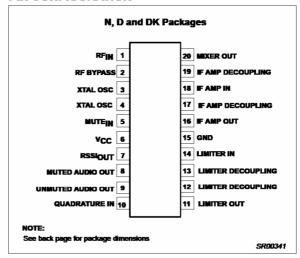

#### PIN CONFIGURATION

Figure 1. Pin Configuration

- Excellent sensitivity: 0.22μV into 50Ω matching network for 12dB SINAD (Signal to Noise and Distortion ratio) for 1kHz tone with RF at 45MHz and IF at 455kHz

- SA615 meets cellular radio specifications

- ESD hardened

#### **APPLICATIONS**

- Cellular radio FM IF

- High performance communications receivers

- Single conversion VHF/UHF receivers

- SCA receivers

- RF level meter

- Spectrum analyzer

- Instrumentation

- FSK and ASK data receivers

- Log amps

- Wideband low current amplification

#### **ORDERING INFORMATION**

| DESCRIPTION                                        | TEMPERATURE RANGE | ORDER CODE | DWG #    |

|----------------------------------------------------|-------------------|------------|----------|

| 20-Pin Plastic Dual In-Line Package (DIP)          | 0 to +70°C        | NE615N     | SOT146-1 |

| 20-Pin Plastic Dual In-Line Package (DIP)          | -40 to +85°C      | SA615N     | SOT146-1 |

| 20-Pin Plastic Small Outline Large (SOL) package   | 0 to +70°C        | NE615D     | SOT108-1 |

| 20-Pin Plastic Small Outline Large (SOL) package   | -40 to +85°C      | SA615D     | SOT108-1 |

| 20-Pin Plastic Shrink Small Outline Package (SSOP) | 0 to +70°C        | NE615DK    | SOT266-1 |

| 20-Pin Plastic Shrink Small Outline Package (SSOP) | -40 to +85°C      | SA615DK    | SOT266-1 |

1992 Nov 3 6–46 853–1402 08109

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013   |

|-----------------------------------------------------------|-----------|----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN6/21 |

Philips Semiconductors Product specification

#### High performance low power mixer FM IF system

**NE/SA615**

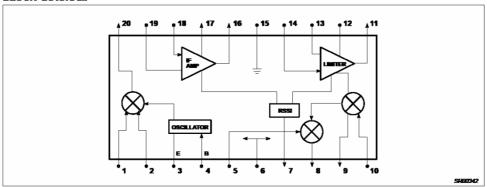

#### **BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL          | PARAMETER                                                | RATING          | UNITS |

|-----------------|----------------------------------------------------------|-----------------|-------|

| Vcc             | Single supply voltage                                    | 9               | V     |

| TSTG            | Storage temperature range                                | -65 to +150     | ℃     |

| TA              | Operating ambient temperature range NE615                | 0 to +70        | °C    |

|                 | SA615                                                    | -40 to +85      | °C    |

| 9 <sub>TV</sub> | Thermal impedance D package<br>N package<br>SSOP package | 90<br>75<br>117 | "C/W  |

#### DC ELECTRICAL CHARACTERISTICS

$V_{CC} = +6V$ ,  $T_A = 25^{\circ}C$ ; unless otherwise stated.

|        |                                  |                 |     | LIMITS   |     |       |

|--------|----------------------------------|-----------------|-----|----------|-----|-------|

| SYMBOL | PARAMETER                        | TEST CONDITIONS |     | NE/SA615 |     | UNITS |

|        |                                  |                 | MEN | TYP      | MAX |       |

| Vcc    | Power supply voltage range       |                 | 4.5 |          | 0.8 | v     |

| lcc    | DC current drain                 |                 |     | 5.7      | 7.4 | mA    |

|        | Mute switch input threshold (ON) |                 | 1.7 |          |     | v     |

|        | (OFF)                            |                 |     |          | 1.0 | v     |

#### **CIRCUIT DESCRIPTION**

The NE/SA615 is an IF signal processing system suitable for second IF or single conversion systems with input frequency as high as 1GHz. The bandwidth of the IF amplifier is about 40MHz, with 39.7dB(v) of gain from a  $50\Omega$  source. The bandwidth of the limiter is about 28MHz with about 62.5dB(v) of gain from a  $50\Omega$  source.

However, the gain/bandwidth distribution is optimized for 455kHz,  $1.5 \mathrm{k}\Omega$  source applications. The overall system is well-suited to battery operation as well as high performance and high quality products of all types.

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013   |

|-----------------------------------------------------------|-----------|----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN7/21 |

Philips Semiconductors Product specification

### High performance low power mixer FM IF system

**NE/SA615**

#### **AC ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}C$ ;  $V_{CC} = +6V$ , unless otherwise stated. RF frequency = 45MHz + 14.5dBV RF input step—up; IF frequency = 455kHz; R17 = 5.1k; RF level = -45dBm; FM modulation = 1kHz with  $\pm$ 8kHz peak deviation. Audio output with C-message weighted filter and de-emphasis capacitor. Test circuit Figure 3. The parameters listed below are tested using automatic test equipment to assure consistent electrical characteristics. The limits do not represent the ultimate performance limits of the device. Use of an optimized RF layout will improve many of the listed parameters.

|                 |                                             |                                            | LIMITS |            | _                                           |                  |

|-----------------|---------------------------------------------|--------------------------------------------|--------|------------|---------------------------------------------|------------------|

| SYMBOL          | . PARAMETER                                 | TEST CONDITIONS                            |        | NE/SA615   | MAX  Mi- Mi- Mi- Mi- Mi- Mi- Mi- Mi- Mi- Mi | UNITS            |

|                 |                                             |                                            | MIN    | TYP        | MAX                                         | 7                |

| Mixer/Osc       | section (ext LO = 300mV)                    | •                                          |        |            |                                             |                  |

| f <sub>IN</sub> | Input signal frequency                      |                                            |        | 500        |                                             | MHz              |

| fosc            | Crystal oscillator frequency                |                                            |        | 150        |                                             | MHz              |

|                 | Noise figure at 45MHz                       |                                            |        | 5.0        |                                             | dB               |

|                 | Third-order input intercept point           | f1 = 45.00; f2 = 45.06MHz                  |        | -12        |                                             | dBm              |

|                 | Conversion power gain                       | Matched 14.5dBV step-up                    | 8.0    | 13         |                                             | dB               |

|                 |                                             | 50Ω source                                 |        | -1.7       |                                             | dB               |

|                 | RF input resistance                         | Single-ended input                         | 3.0    | 4.7        |                                             | kΩ               |

|                 | RF input capacitance                        |                                            |        | 3.5        | 4.0                                         | pF               |

|                 | Mixer output resistance                     | (Pin 20)                                   | 1.25   | 1.50       |                                             | kΩ               |

| IF section      |                                             |                                            |        |            |                                             |                  |

|                 | IF amp gain                                 | 50Ω source                                 |        | 39.7       |                                             | dB               |

|                 | Limiter gain                                | 50Ω source                                 |        | 62.5       |                                             | dB               |

|                 | Input limiting -3dB, R <sub>17</sub> = 5.1k | Test at Pin 18                             |        | -109       |                                             | dBm              |

|                 | AM rejection                                | 80% AM 1kHz                                | 25     | 33         | 43                                          | dB               |

|                 | Audio level, R <sub>10</sub> = 100k         | 15nF de-emphasis                           | 60     | 150        | 260                                         | mV <sub>RM</sub> |

|                 | Unmuted audio level, R <sub>11</sub> = 100k | 150pF de-emphasis                          |        | 530        |                                             | m∨               |

|                 | SINAD sensitivity                           | RF level -118dB                            |        | 12         |                                             | dB               |

| THD             | Total harmonic distortion                   |                                            | -30    | -42        |                                             | dB               |

| S/N             | Signal-to-noise ratio                       | No modulation for noise                    |        | 68         |                                             | dB               |

|                 | IF RSSI output, $R_9 = 100k\Omega^1$        | IF level = -118dBm                         | 0      | 160        | 800                                         | mV               |

|                 |                                             | IF level = -68dBm                          | 1.7    | 2.5        | 3.3                                         | V                |

|                 |                                             | IF level = -18dBm                          | 3.6    | 4.8        | 5.8                                         | V                |

|                 | RSSI range                                  | R <sub>9</sub> = 100kΩ Pin 16              |        | 80         |                                             | dB               |

|                 | RSSI accuracy                               | R <sub>9</sub> = 100kΩ Pin 16              |        | <u>+</u> 2 |                                             | dB               |

|                 | IF input impedance                          |                                            | 1.40   | 1.6        |                                             | kΩ               |

|                 | IF output impedance                         |                                            | 0.85   | 1.0        |                                             | kΩ               |

|                 | Limiter intput impedance                    |                                            | 1.40   | 1.6        |                                             | kΩ               |

|                 | Unmuted audio output resistance             |                                            |        | 58         |                                             | kΩ               |

|                 | Muted audio output resistance               |                                            |        | 58         |                                             | kΩ               |

| RF/IF sect      | tion (int LO)                               | -                                          |        | -          | -                                           | _                |

|                 | Unmuted audio level                         | 4.5V = V <sub>CC</sub> , RF level = -27dBm |        | 450        |                                             | mV <sub>RM</sub> |

|                 | System RSSI output                          | 4.5V = V <sub>CC</sub> , RF level = -27dBm |        | 4.3        |                                             | V                |

#### NOTE:

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013   |

|-----------------------------------------------------------|-----------|----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN8/21 |

The generator source impedance is 50Ω, but the NE/SA605 input impedance at Pin 18 is 1500Ω. As a result, IF level refers to the actual signal that enters the NE/SA605 input (Pin 8) which is about 21dB less than the "available power" at the generator.

#### **DATA SHEET**

# BIPOLAR DIGITAL INTEGRATED CIRCUITS $\mu PB1506GV$ , $\mu PB1507GV$

# 3GHz INPUT DIVIDE BY 256, 128, 64 PRESCALER IC FOR ANALOG DBS TUNERS

The  $\mu$ PB1506GV and  $\mu$ PB1507GV are 3.0 GHz input, high division silicon prescaler ICs for analog DBS tuner applications. These ICs divide-by-256, 128 and 64 contribute to produce analog DBS tuners with kit-use of 17 K series DTS controller or standard CMOS PLL synthesizer IC. The  $\mu$ PB1506GV/ $\mu$ PB1507GV are shrink package versions of the  $\mu$ PB586G/588G or  $\mu$ PB1505GR so that these smaller packages contribute to reduce the mounting space replacing from conventional ICs.

The  $\mu$ PB1506GV and  $\mu$ PB1507GV are manufactured using NEC's high fr NESAT<sup>TM</sup>IV silicon bipolar process. This process uses silicon nitride passivation film and gold electrodes. These materials can protect chip surface from external pollution and prevent corrosion/migration. Thus, these ICs have excellent performance, uniformity and reliability.

#### **FEATURES**

High toggle frequency : fin = 0.5 GHz to 3.0 GHz

High-density surface mounting : 8-pin plastic SSOP (175 mil)

Low current consumption : 5 V, 19 mA

Selectable high division : ±256, ±128, ±64

- Pin connection variation : μPB1506GV and μPB1507GV

#### **APPLICATION**

These ICs can use as a prescaler between local oscillator and PLL frequency synthesizer included modulus prescaler. For example, following application can be chosen;

- Analog DBS tuner's synthesizer

- · Analog CATV converter synthesizer

#### **ORDERING INFORMATION**

| PART NUMBER  | PACKAGE        | MARKING | SUPPLYING FORM                                     |

|--------------|----------------|---------|----------------------------------------------------|

| μPB1506GV-E1 | 8-pin plastic  | 1506    | Embossed tape 8 mm wide. Pin 1 is in tape pull-out |

| μPB1507GV-E1 | SSOP (175 mil) | 1507    | direction. 1 000 p/reel.                           |

Remarks To order evaluation samples, please contact your local NEC sales office.

(Part number for sample order: μPB1506GV, μPB1507GV)

Caution: Electro-static sensitive devices

Document No. P10767EJ3V0DS00 (3rd edition)

Date Published January 1998 N CP(K)

Printed in Japan

© NEC Corporation 1996

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013   |

|-----------------------------------------------------------|-----------|----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN9/21 |

#### PIN CONNECTION (Top View)

| Pin<br>NO. | μPB1506GV | μPB1507GV |

|------------|-----------|-----------|

| 1          | SW1       | IN        |

| 2          | IN        | Vcc       |

| 3          | ĪN        | SW1       |

| 4          | GND       | OUT       |

| 5          | NC        | GND       |

| 6          | SW2       | SW2       |

| 7          | ОИТ       | NC        |

| 8          | Vcc       | ĪN        |

#### PIN EXPLANATION

|          | Applied      | Pin          |                                                                                                                        | F                                                                                                                | £      |           |            |                          | Pin               | no.       |

|----------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|-----------|------------|--------------------------|-------------------|-----------|

| Pin name | voltage<br>V | voltage<br>V |                                                                                                                        | Funk                                                                                                             | lions  | and expla | anauon     |                          | <i>µ</i> РВ1506GV | µРВ1507GV |

| IN       | _            | 2.9          | Signal inpu                                                                                                            | •                                                                                                                | •      |           | •          | ed to signal<br>C cut.   | 2                 | 1         |

| ĪN       |              | 2.9          | Signal input bypass pin. This pin must be equipped with bypass capacitor (e.g. 1 000 pF) to minimize ground impedance. |                                                                                                                  |        |           |            | 3                        | 8                 |           |

| GND      | 0            |              | formed as                                                                                                              | Ground pin. Ground pattern on the board should be formed as wide as possible to minimize ground impedance.       |        |           |            |                          | 4                 | 5         |

| SW1      | H/L          | _            | ı                                                                                                                      | Divide ratio input pin. The ratio can be determined by following applied level to these pins.                    |        |           |            | 1                        | 3                 |           |

|          |              |              | [                                                                                                                      |                                                                                                                  |        | SV        | <b>V</b> 2 |                          |                   |           |

|          |              |              |                                                                                                                        |                                                                                                                  |        | Н         | L          |                          |                   |           |

| SW2      |              |              |                                                                                                                        | SW1                                                                                                              | н      | ÷64       | ÷128       |                          | 6                 | 6         |

|          |              |              | [                                                                                                                      |                                                                                                                  | L      | ÷128      | ÷256       |                          |                   |           |

|          |              |              | These pins<br>(e.g. 1 000                                                                                              |                                                                                                                  | •      | • •       |            | s capacitor<br>nce.      |                   |           |

| Vcc      | 4.5 to 5.5   | _            | bypass car                                                                                                             | Power supply pin. This pin must be equipped with bypass capacitor (e.g. 10 000 pF) to minimize ground impedance. |        |           |            |                          | 8                 | 2         |

| ОИТ      | _            | 2.6 to 4.7   | Divided fre<br>emitter follo<br>CMOS inpo                                                                              | ower out                                                                                                         | put T  | his pin c | an be co   | esigned as<br>nnected to | 7                 | 4         |

| NC       | _            | _            | Non conne                                                                                                              | ction pin                                                                                                        | . This | pin mus   | t be ope   | nned.                    | 5                 | 7         |

| BTS SYSTÈMES ÉLECTRONIQUES – Étude d'un Système Technique |           | Session 2013    |

|-----------------------------------------------------------|-----------|-----------------|

| U4.1 – Électronique – Documentation                       | 13SEE4EL1 | Page : BAN10/21 |

# **UPC2709T, UPC2712T**

# 2.5 GHz SILICON MMIC WIDE-BAND AMPLIFIER

#### **FEATURES**

- WIDE FREQUENCY RESPONSE: 2.5 GHz

- HIGH GAIN: 23 dB (UPC2709T)

- SATURATED OUTPUT POWER: +11.5 dBm (UPC2709T)

- INTERNAL CURRENT REGULATION MINIMIZES GAIN CHANGE OVER TEMPERATURE

- 5 V SINGLE SUPPLY VOLTAGE

- SUPER SMALL PACKAGE

- TAPE AND REEL PACKAGING OPTION AVAILABLE

#### **DESCRIPTION**

NEC's UPC2709T and UPC2712T are Silicon Monolithic integrated circuits manufactured using the NESAT III process. These devices are suitable as buffer amplifiers for wide-band applications. They are designed for low cost gain stages in cellular radios, GPS receivers, DBS tuners, PCN, and test/measurement equipment.

NEC's stringent quality assurance and test procedures ensure the highest reliability and performance.

#### ELECTRICAL CHARACTERISTICS (TA = 25°C, f = 1 GHz, Vcc = 5 V)